隨著移動設備、物聯網和便攜式電子產品的快速發展,模擬集成電路(Analog Integrated Circuits, AICs)在低電壓系統中的應用日益廣泛。低電壓電源設計不僅關系到系統的功耗和效率,還直接影響電路的性能和可靠性。本文將探討模擬集成電路中低電壓系統的電源設計原則、關鍵挑戰以及實際應用場景。

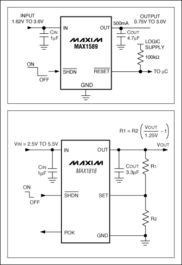

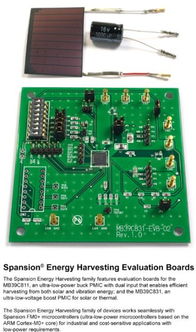

低電壓系統電源設計的核心目標是降低功耗,延長電池壽命,同時保持信號處理的精度和動態范圍。在模擬集成電路中,電源電壓的降低會帶來諸多挑戰,例如噪聲敏感性增加、線性度下降以及工藝變異性影響放大。因此,設計時需考慮采用低功耗架構,如使用開關電容器電路或電流模式技術,以減少靜態電流并優化動態性能。電源管理單元(PMU)的集成至關重要,它可以通過調節電壓和電流來適應不同工作模式,確保系統在待機和活躍狀態下的高效運行。

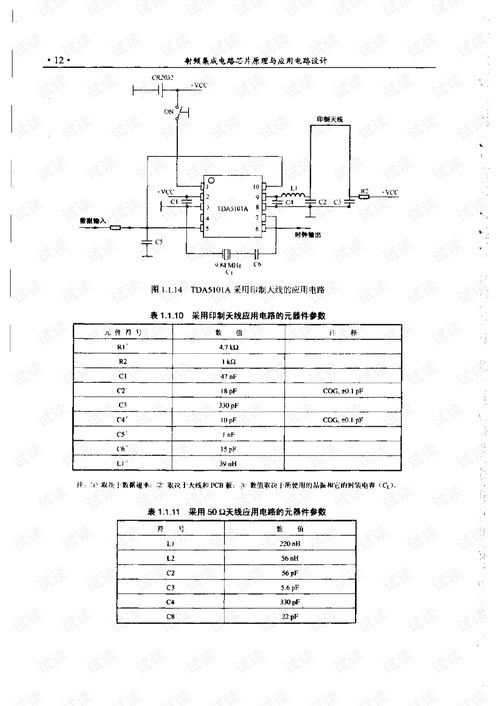

在低電壓電源設計中,噪聲抑制和電源抑制比(PSRR)是關鍵因素。模擬電路對電源噪聲非常敏感,尤其是在低電壓下,噪聲可能顯著影響信號的信噪比。為此,設計師常采用片上穩壓器、濾波電容和布局優化技術來最小化噪聲干擾。同時,選擇適合的低功耗工藝節點,如CMOS技術,可以幫助降低漏電流并提高整體效率。在實際應用中,例如在傳感器接口或音頻處理電路中,這些設計策略能夠確保電路在低電壓下仍能提供穩定的輸出。

低電壓模擬集成電路的電源設計在多個領域有廣泛應用。在醫療設備中,如可穿戴健康監測器,低電壓系統能實現長時間連續工作;在工業自動化中,它支持傳感器網絡的節能運行;而在消費電子領域,智能手機和無線耳機則依賴這些設計來提升電池續航。未來,隨著半導體技術的進步,低電壓電源設計將朝著更高集成度、更智能的電源管理方向發展,推動模擬集成電路在能效和性能上的突破。

模擬集成電路的低電壓系統電源設計是一個復雜但關鍵的領域,它要求設計師在功耗、噪聲和可靠性之間找到平衡。通過創新的電路架構和工藝優化,我們可以實現更高效、更可靠的電子系統,滿足現代應用的多樣化需求。